Report Delivered for this project here

This entry records the steps taken after the above report was delivered.

BookSeeBookSee

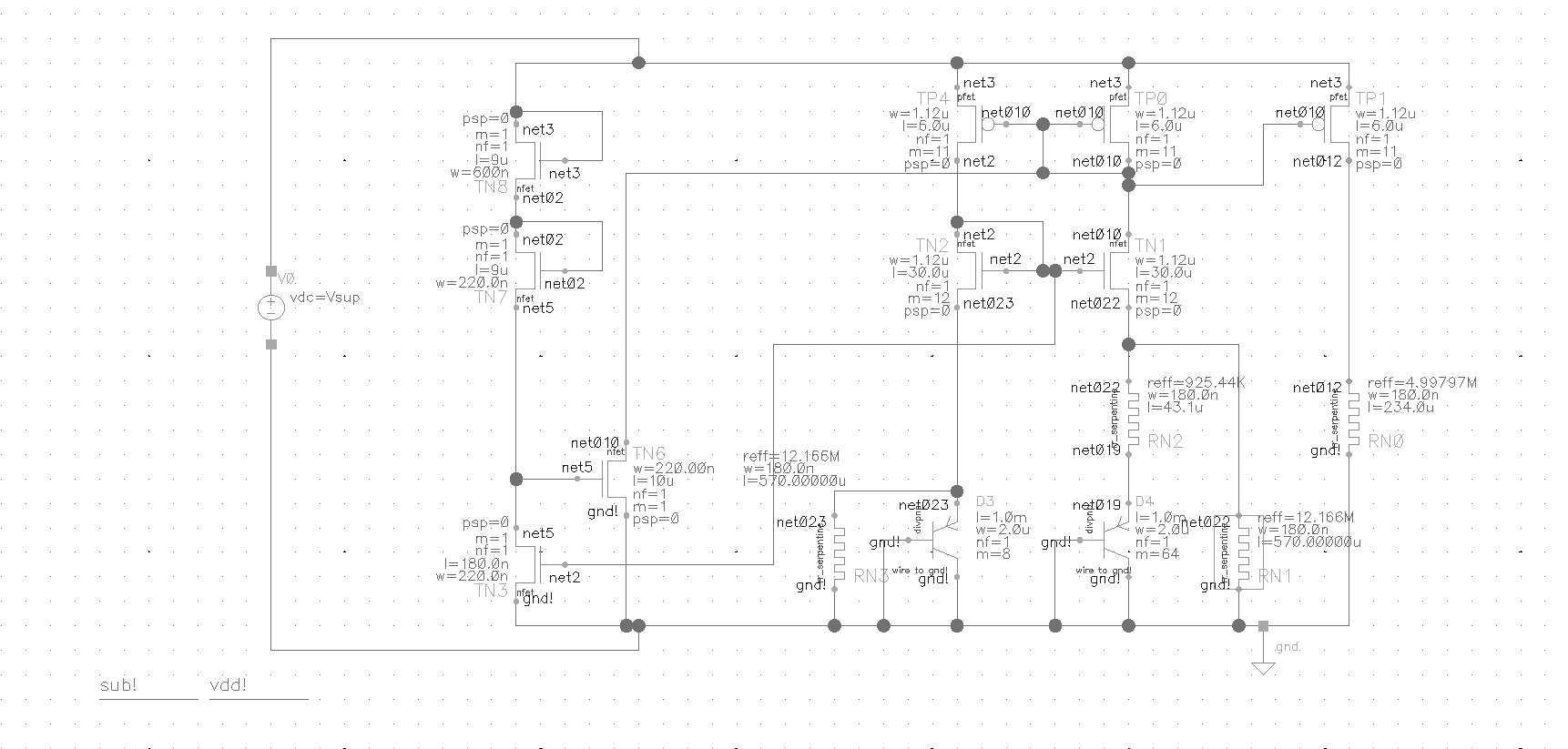

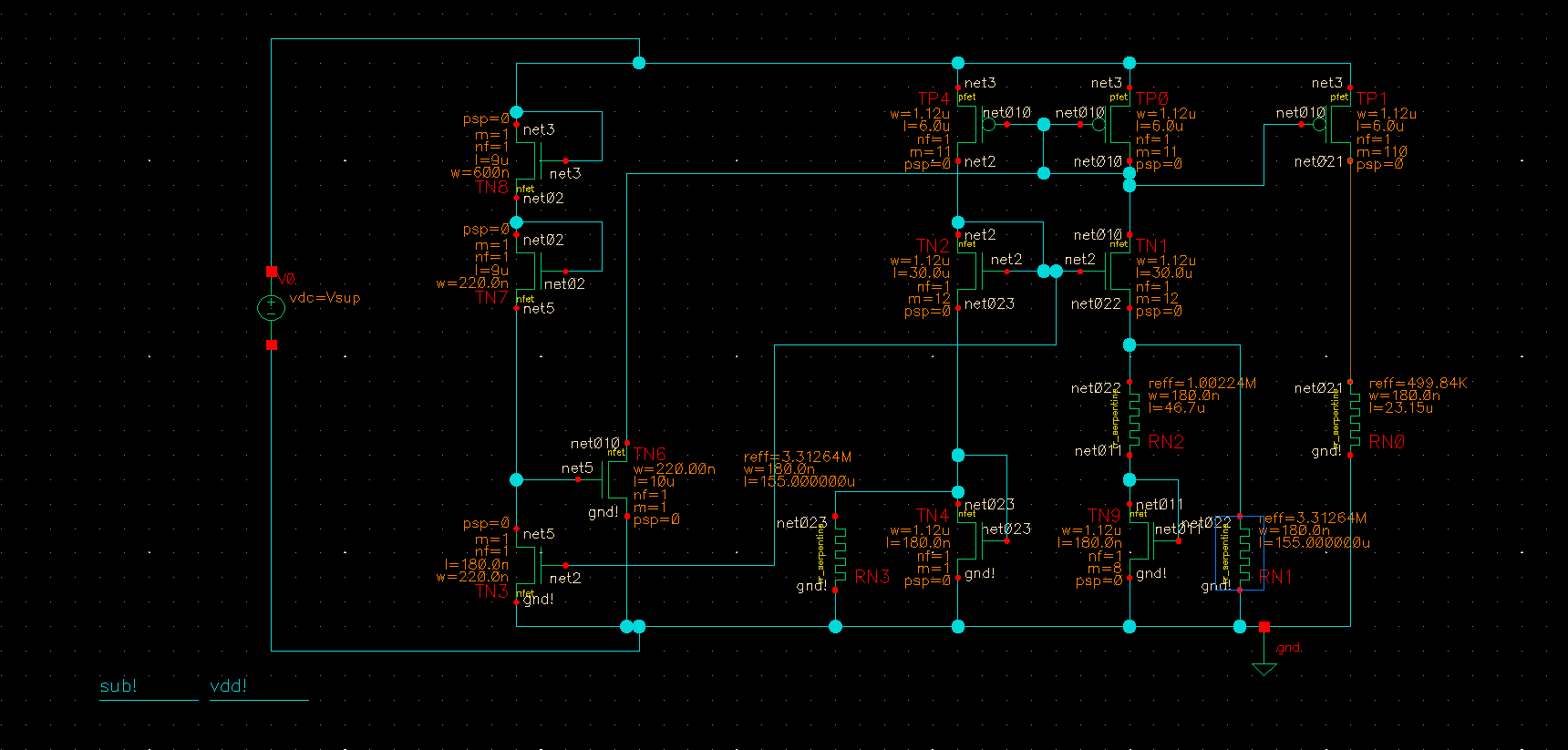

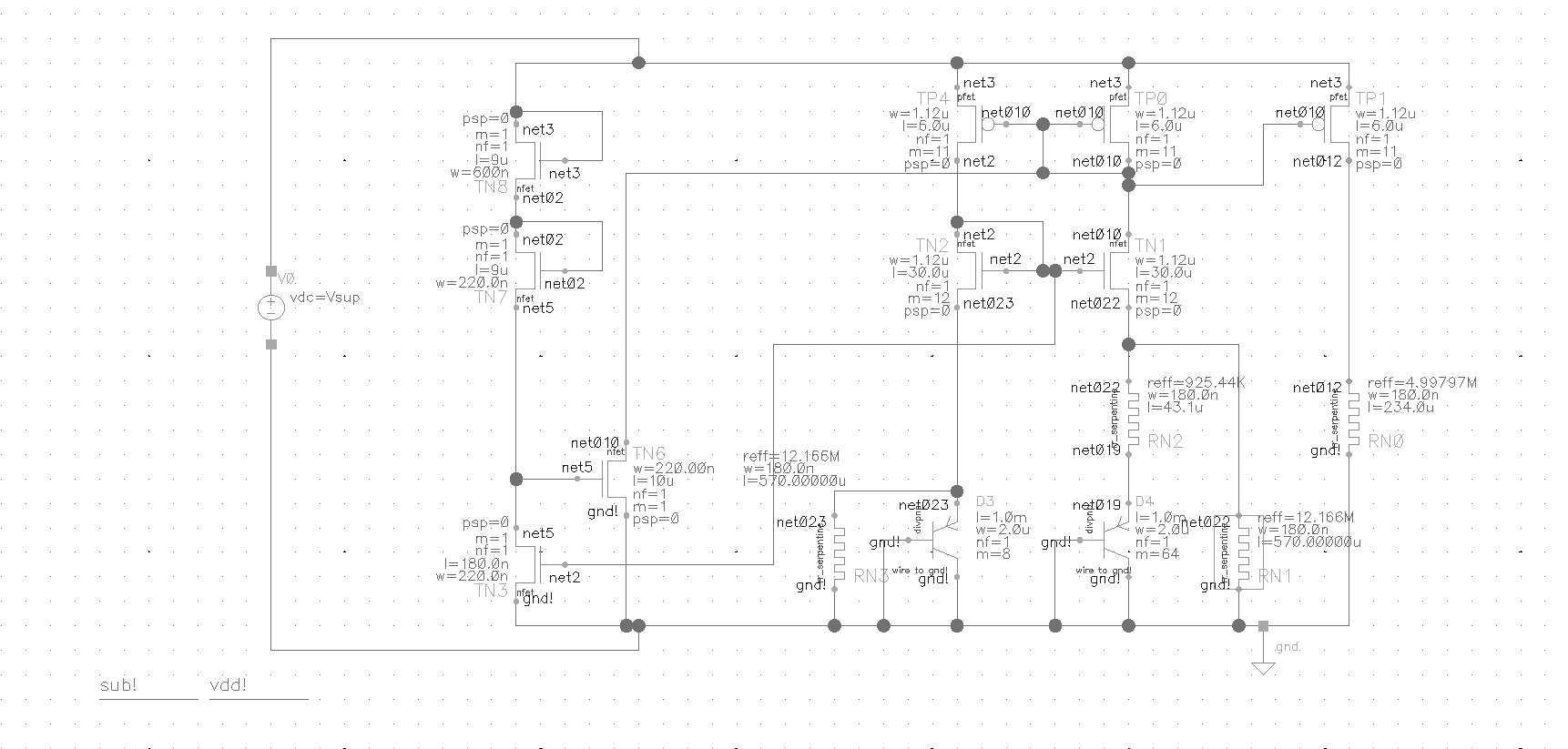

TN3 was too long previous to this fix. Thus TN5 was not shutting off sufficiently and drawing too much current off of the current mirror.

Next Steps:

-

Redo startup transient analysisResearch Links

-

Redo Monte Carlo analysis including startup circuit

-

Go over the circuit for any possible reduction in sizes in the diodes and resistors.

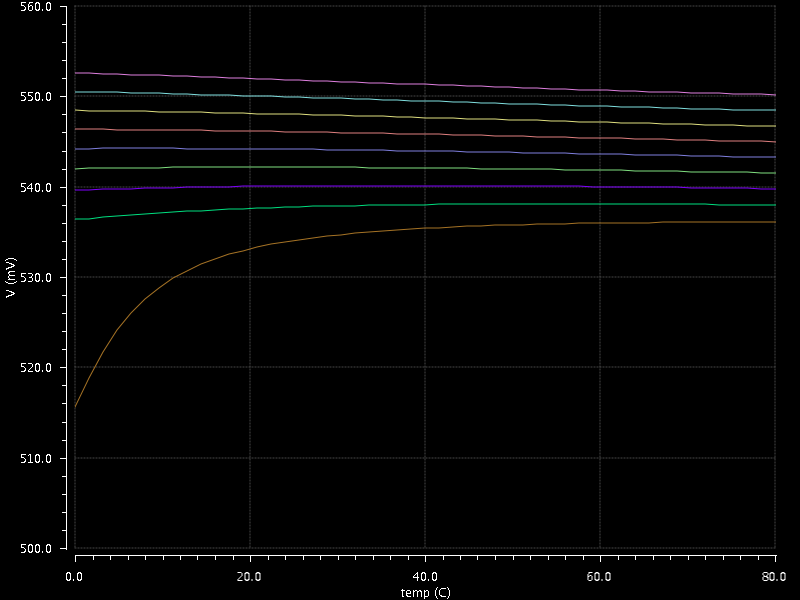

Transient Analysis Redo Results

-

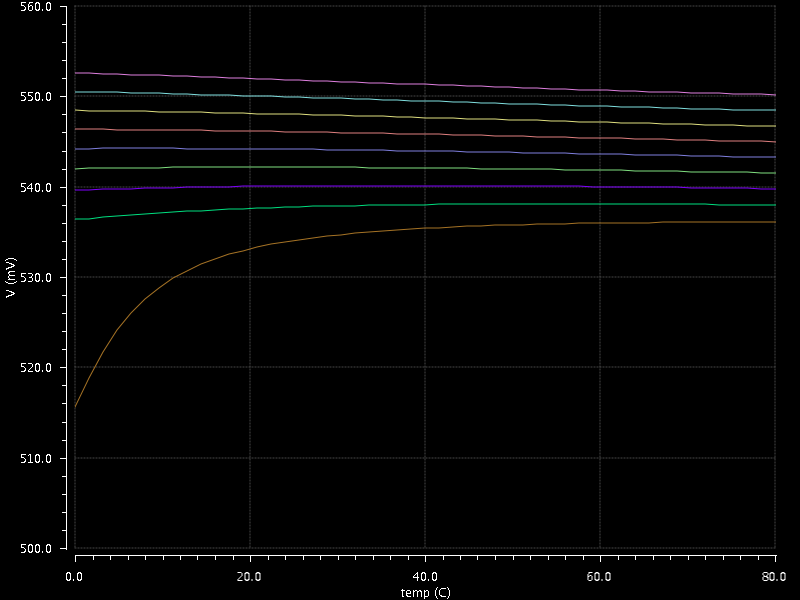

1 to 1.8V supply voltage in 0.1 Volt steps.

-

About 0.5 mSec to turn on

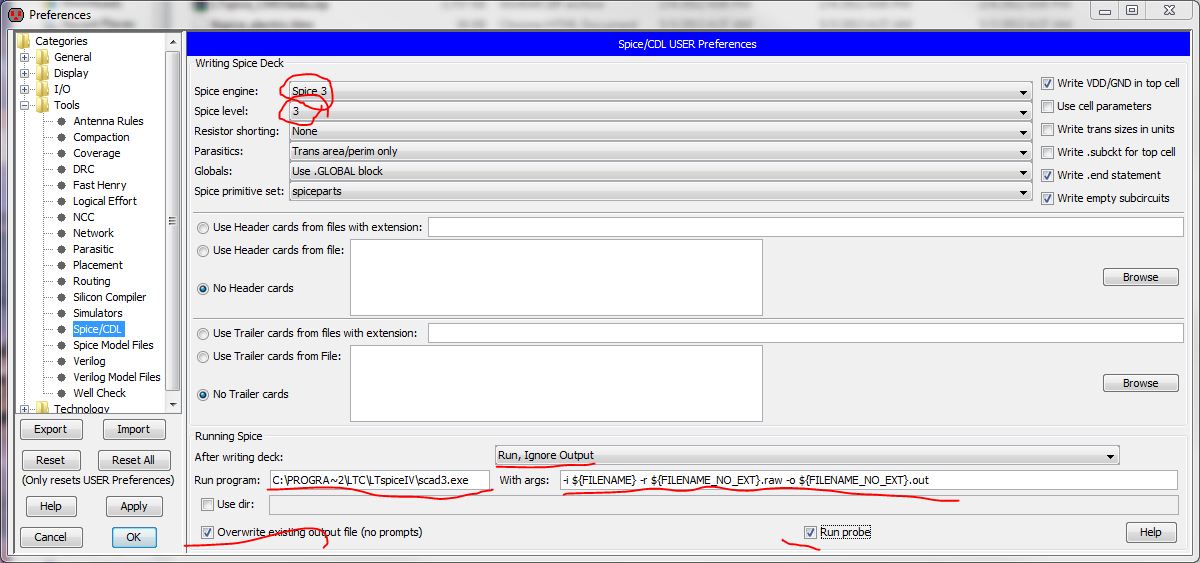

Tweaking Monte Carlo V2 for output concavityResearch Links

Research 0L0inks

Tweaking Monte Carlo V2 for output concavity

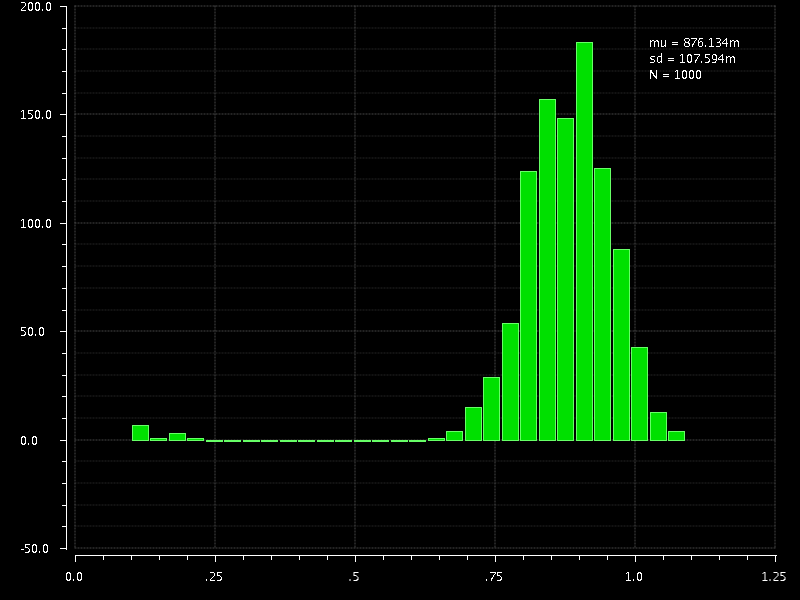

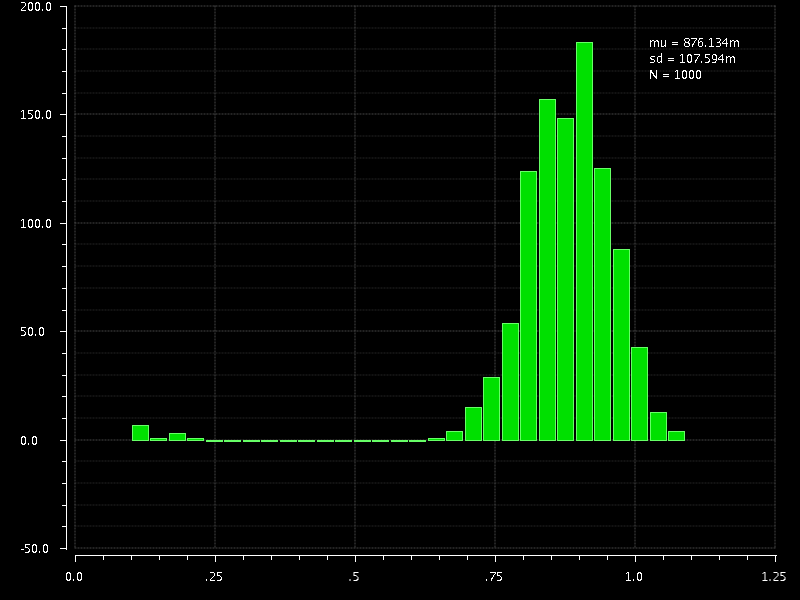

Round Two Monte Carlo Results

Research Links

Research Links

-

968 in the desired working range

-

32 versions exhibited in the bins: 47,62,93 mV

Preliminary Layout

-

The big rectangles are the diode connected bjt's

-

The little rectangles are the FETS

-

The long thin red lines are the resistors

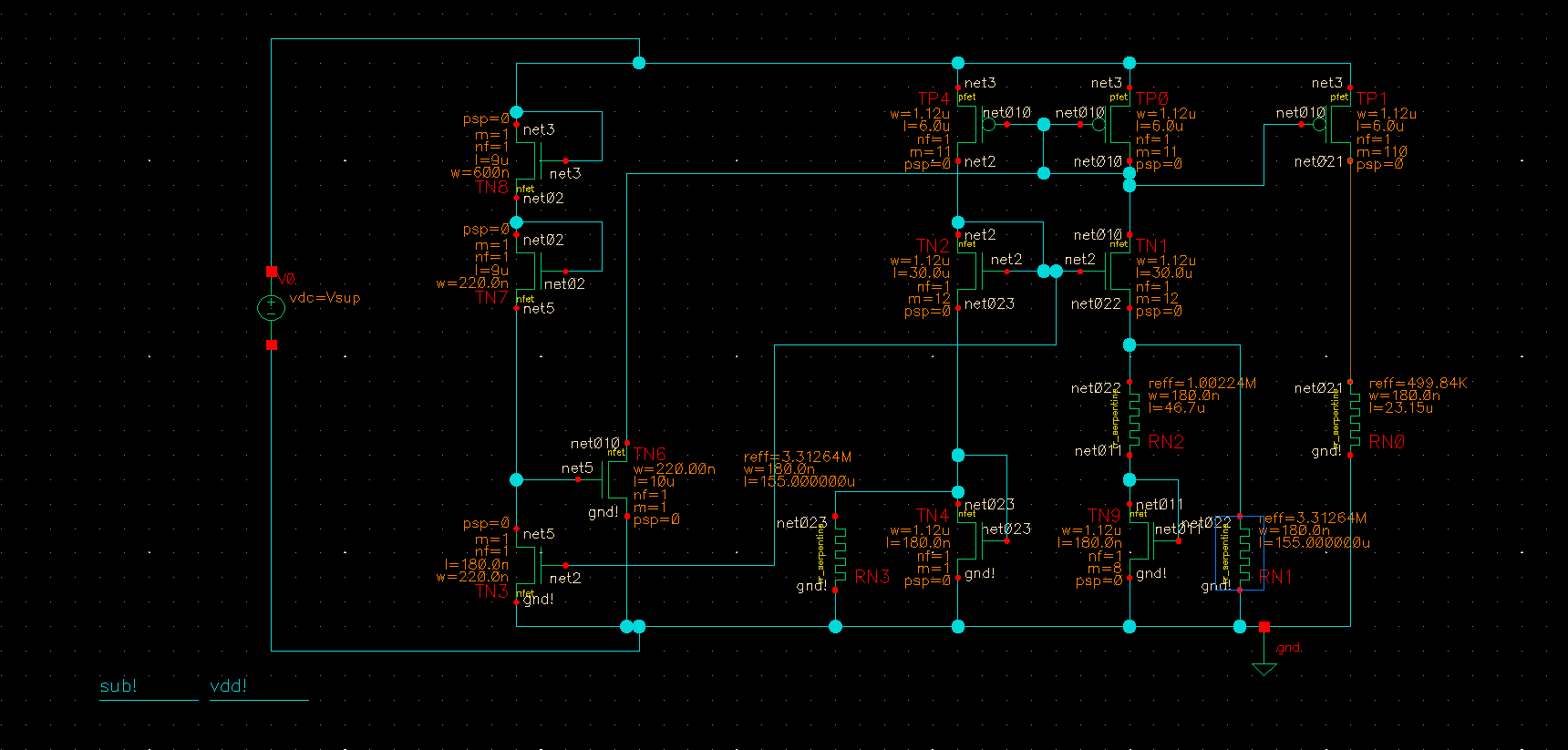

FETs as Diodes

-

One way around the huge diodes would be to use nmos fets in weak inversion and diode connected. Their characteristic is exponential under these circumstances and the worst case threshold voltage is 150mV less than the huge diode drop. I am not sure if this is practical or not in actual practice but the simulation below looks good.

-

Resistor values had to be altered. The large resistors can be reduced from around 12 MOhm down to about 3 MOhm.

-

The FET mismatch leads to the following Monte Carlo distribution. Looks like I need to make the "diode" FETs bigger.

DIPDNW in the diode position

-

Appears to be 1/60 the area of the divpnp version

Monte Carlo Analysis @T=27 degrees C shows it well behaved more or less. Still has issue with startup at times.

Monte Carlo Analysis @T=80 degrees C shows it well behaved. Distribution at the low end it gone.

Monte Carlo Analysis @T=0 degrees C shows markedly more false starts than higher temperatures

ac

ac

Research Links

Research Links

ac

ac