Current Mode Logic and Prescaler Project Notes

|

Project Report: Please note I ran out of time so the organization and writing of this report is lacking. It does cover the basics of designing an 8/9 dual modulus prescaler. |

If you improve upon this report please come back to this post and put a link to your improved version in the comments.

Research Links: CML Prescaler

- An Analysis of MOS Current Mode Logic for Low Power and High Performance Digital Logic

- A LOW POWER PRESCALER, PHASE FREQUENCY DETECTOR, AND CHARGE PUMP FOR A 12 GHZ FREQUENCY SYNTHESIZER – Evan Lee Eschenko – has a basic cml gate

- A Dynamic-Logic Frequency Divider for 5-GHz WLAN Frequency Synthesizer

- Design of MOS Current-Mode Logic Standard Cells Technology: NSC 0.18 µm CMOS9

- High-Speed CMOS Dual-Modulus Prescalers for Frequency Synthesis by Ranganathan Desikachari

- NEW CML LATCH STRUCTURE FOR HIGH SPEED PRESCALER DESIGN

- A 3.8-mW 2.5-GHz Dual-Modulus Prescaler in a 0.8 µm Silicon Bipolar Production Technology

- ECEN620: Network Theory Broadband Circuit Design

- High Speed Communication Circuits and Systems – Lecture 14 – High Speed Frequency Dividers

- Design of a 5.8 GHz Multi-Modulus Prescaler – Good discussion of how multi modulus prescaler works – block level state machine

- Frequency Dividers – Jri Lee

- Generalized Multi Modulus Dividers using 2/3 cells

- A 1.8V, 3GHz 16/17 Dual Modulus Prescaler in 0.35µm CMOS Technology – has merged Nand D Flip Flop, D Flip Flop and Merged 3-input AND & NAND D-FF topologies for the architecture realization

- A New Dual-Modulus Divider Circuit Technique – I like the way he draws the CML logic block diagrams

Research Links: CML to CMOS converter circuit

This lecture talks about how you need a level shifter for transistor inputs lower on the input ladder of CML logic.

Support Links

- lecture7 – Current mode logic – MUX, XOR, Latch

- lecture8 – Current mode logic – Latch design

- IIT Video Lectures on VLSI Broadband Communication Circuits by Prof. Nagendra Krishnapura

- 74HC193 presettable up / down counter LTSPICE files

- Binary Counter

- Avant HSPICE – Performing Behavoiral Modeling – The entire book

- A Digital Frequency Synthesizer Using Phase Locked Loop Technique – Gursharan Reehal

- Pulse swallowing frequency divider with low power and compact structure Has TSPC registers

- High Speed Communication Circuits and Systems – Lecture 14 – High Speed Frequency Dividers

Additional Links

FireChat – FireBase – Smart Phone Mesh Network Application

Research Links

- FireChat

- OpenGarden – but FireChat is proprietary!

- FireBase – FireChat

- FireChat documentation

This application was used in Iraq and Honk Kong when the rulers shut down the internet.

OptoElectronics Projects and Experiments

Research Links

- Measuring the speed of light

- Optical gyro – relativity

- Build a Fiber Optic Gyro Sagnac's paper

- Optical Gates – this is too close to the edge

- Trillionth of Second Camera

- Single Photon Detector of any type

- Single / Double slit experiment with LED / Laser

- Polarized light – LED

- Stress analyzer – birefringence

- Particle manipulation with laser beams – demonstrate forces with light

- demostrate cooling with light

- entangled photons generator

- gravity effect on speed of light / wavelength

- some sort of super accurate clock based on opto electronics

- Transmit audio with a laser pen

- Measure speed of light with a laser

- 3D object measurement tool for shipping estimate etc.

- Raman Spectrometer

- Measuring the width of a human hair with laser interference pattern

Speed of Light Measurement

- Speed of Light with a laser pointer / diode

- Infrared Thermometer assembly

- SENSOR DE LASER PARA MEDIÇÃO DA VELOCIDADE DA LUZ

- Speed of Light with Nanosecond Pulsed 650 nm Diode Laser

- Speed of Light with an IR LED

- Nanosecond Avalanche Transistor Pulse Generator

- Avalanche Pulse generator

- High Speed Amplifier Techniques – A Designer’s Companion for Wideband Circuitry – Jim Williams

- Measurement of speed of light through the ages

2 Color Optical Pyrometer

Side Issues

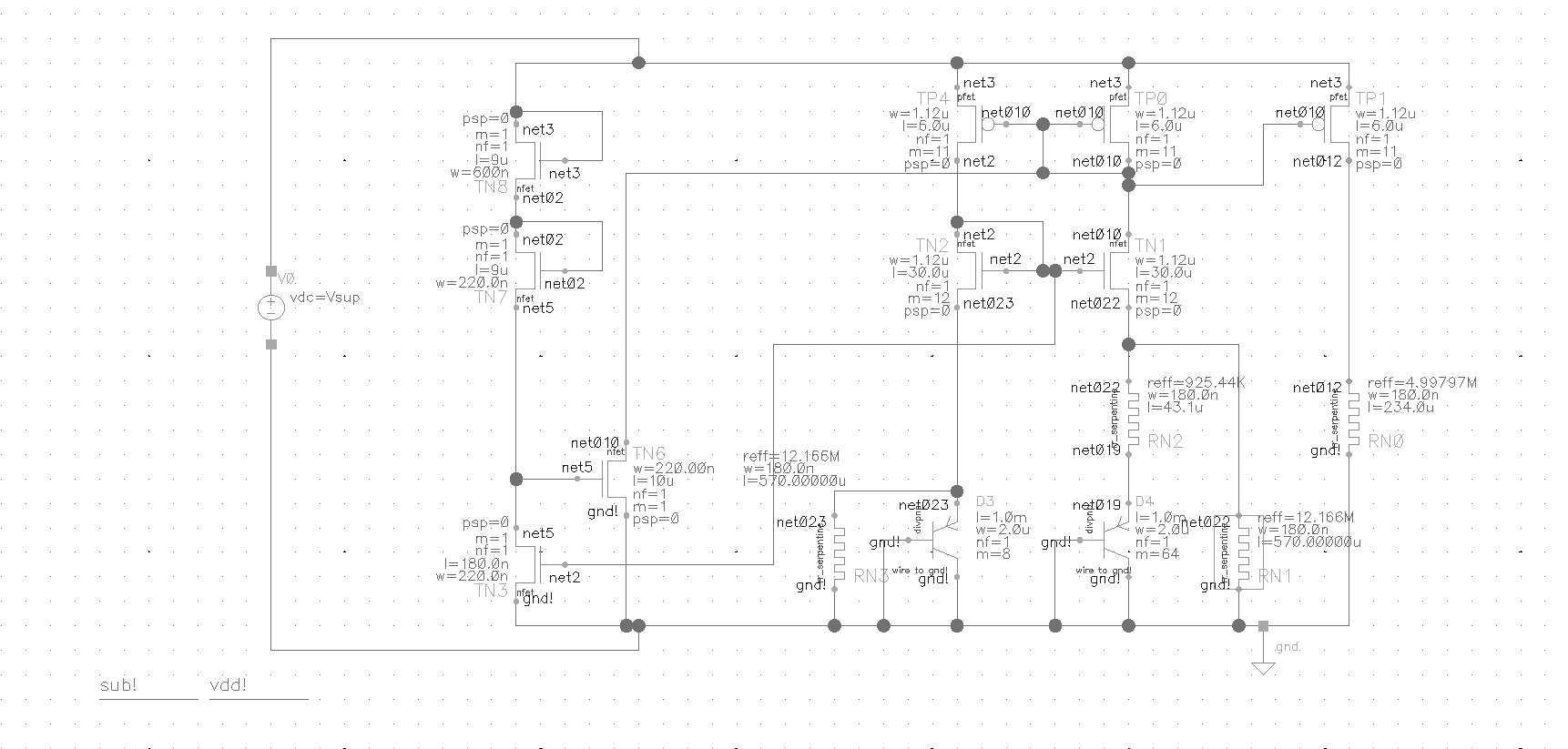

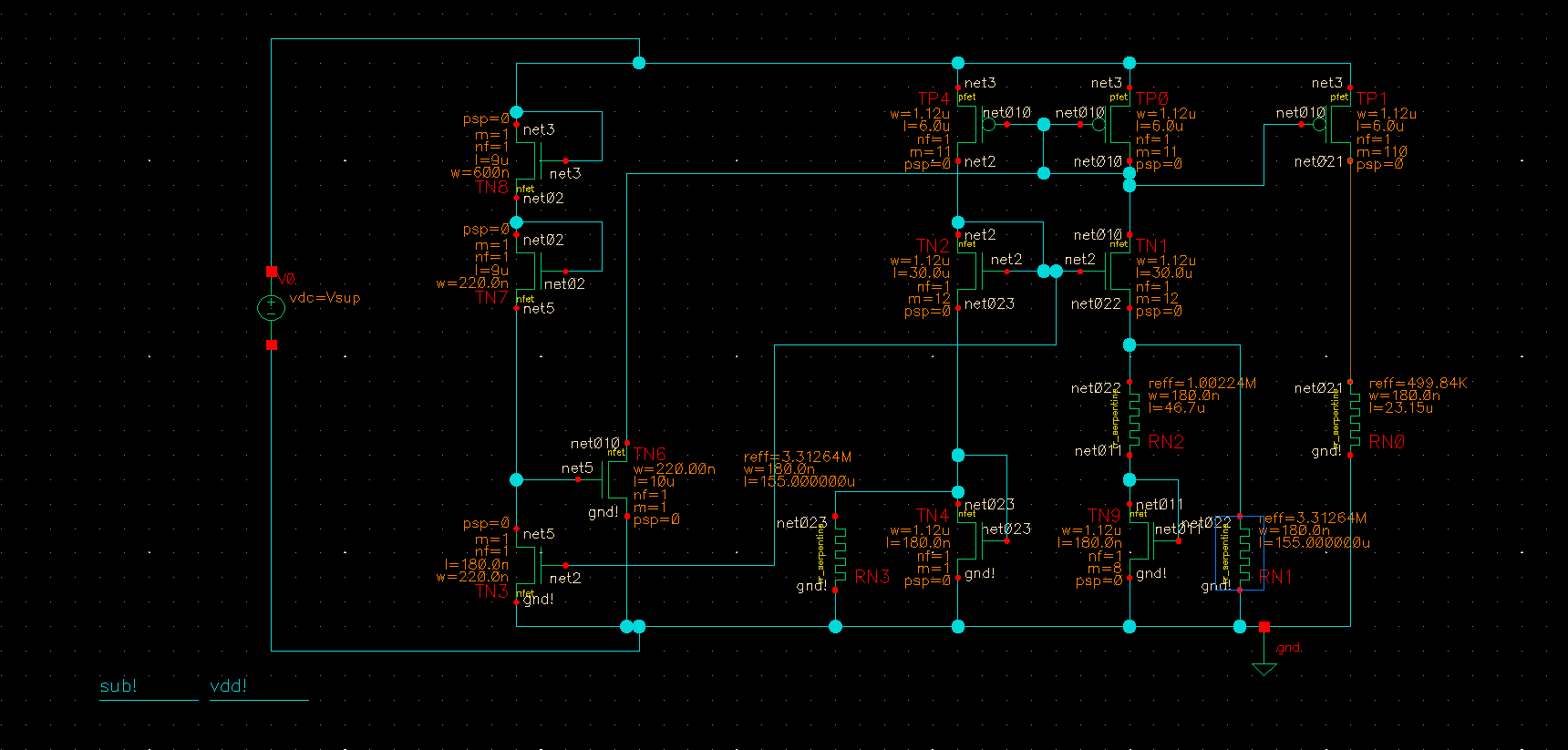

1.2 Volt Band Gap Reference After the Start Up Circuit is fixed

Report Delivered for this project here

This entry records the steps taken after the above report was delivered.

TN3 was too long previous to this fix. Thus TN5 was not shutting off sufficiently and drawing too much current off of the current mirror.

Next Steps:

- Redo startup transient analysisResearch Links

- Redo Monte Carlo analysis including startup circuit

- Go over the circuit for any possible reduction in sizes in the diodes and resistors.

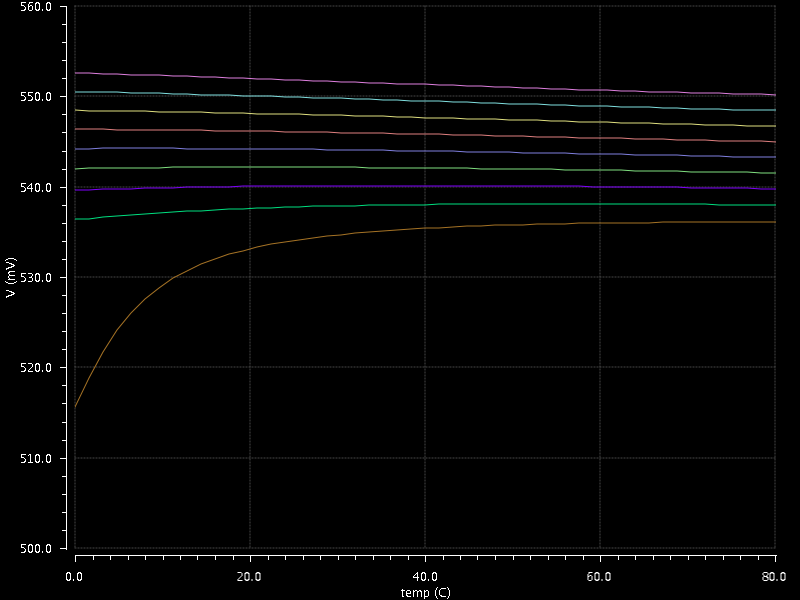

Transient Analysis Redo Results

- 1 to 1.8V supply voltage in 0.1 Volt steps.

- About 0.5 mSec to turn on

Tweaking Monte Carlo V2 for output concavityResearch Links

Research 0L0inks

Tweaking Monte Carlo V2 for output concavity

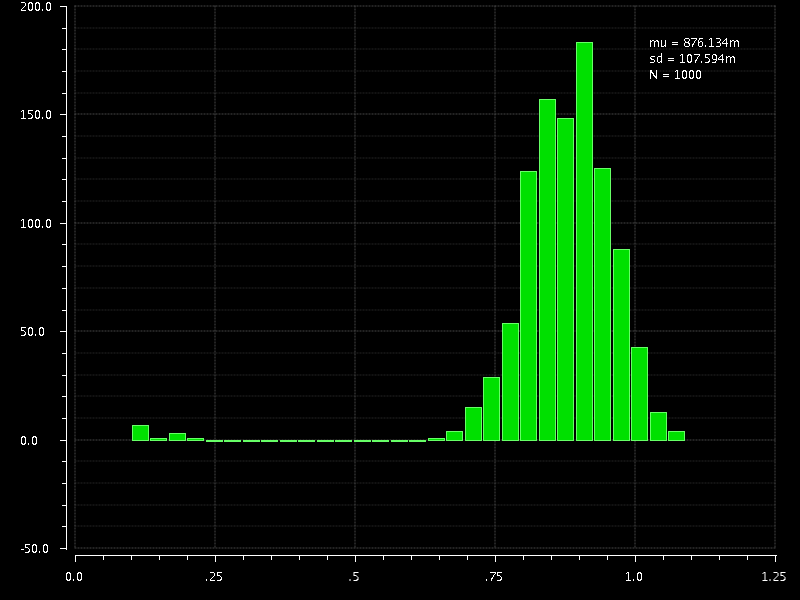

Round Two Monte Carlo Results

Research Links

Research Links

- 968 in the desired working range

- 32 versions exhibited in the bins: 47,62,93 mV

Preliminary Layout

- The big rectangles are the diode connected bjt's

- The little rectangles are the FETS

- The long thin red lines are the resistors

FETs as Diodes

- One way around the huge diodes would be to use nmos fets in weak inversion and diode connected. Their characteristic is exponential under these circumstances and the worst case threshold voltage is 150mV less than the huge diode drop. I am not sure if this is practical or not in actual practice but the simulation below looks good.

- Resistor values had to be altered. The large resistors can be reduced from around 12 MOhm down to about 3 MOhm.

- The FET mismatch leads to the following Monte Carlo distribution. Looks like I need to make the "diode" FETs bigger.

DIPDNW in the diode position

- Appears to be 1/60 the area of the divpnp version

Monte Carlo Analysis @T=27 degrees C shows it well behaved more or less. Still has issue with startup at times.

Monte Carlo Analysis @T=80 degrees C shows it well behaved. Distribution at the low end it gone.

Monte Carlo Analysis @T=0 degrees C shows markedly more false starts than higher temperatures

ac

ac

Importing a Design Library into Cadence Virtuoso

I had a problem where when I returned to my opensuse based machine my Cadence design library was no where to be seen in the library manager. In order to for it to show up again in the list there are 2 ways of approaching the problem.

- With the Log window( not sure what it is called ) click: Tools > Library Path Manager

- or you can directly edit CDS.lib

I think the first method is the way that is intended by the software authors but who can tell with an interface as bad as Cadence?

Android CyanogenMod

Research Links

- CyanogenMod Installer

- confused, does the cyanogenmod installer root my phone or not?

- Google: cyanogenMod phone not rooted

- http://www.cyanogenmod.org/

When they use the term "mod" it leaves one with the impression that the resident ROM code is being mod'd and not completely replaced. However further reading leaves me with the opposite impression.

I am hoping to use it to have root access on my old phone so I can get rid of all the junk applications ATT included on it.